Introduction

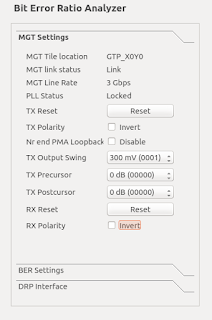

Hi there! Welcome to my blog. About me : I am Harsh Gugale, a senior UG student at Indian Institute of Technology (BHU) Varanasi, pursuing a bachelors degree in Electronics Engg. About Google Summer of Code : Google Summer of Code (GSoC) is a summer internship program by Google where students can work with open source organizations from around the world, contribute to these organizations by either working on existing projects or something entirely new and in turn get paid from Google in doing so! (Cool isn't it?) Organization : I am taking part in GSoC 2018 under TimVideos . TimVideos.us is a group of exciting projects which provide both hardware and software solutions to record and live video stream conferences, meetings, and other presentations. Project : Bit error ratio testers are used to test the quality of signal trans-reception. They are routinely used to test boards with high-speed serial links and tune parameters so that the medium fidelity is maximize...