Progress Report - 2

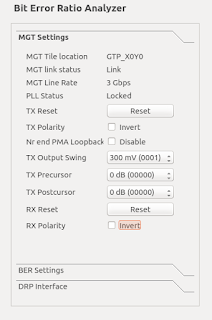

I have completed coding a basic version of Bit Error Ratio Analyser. Features: 1) MGT Settings: 2) BER Settings: 3) DRP Interface Code : 1) All coded files may be found here: https://github.com/harshgugale/ber_analyzer_gtp 2) Litex local install is necessary. Next Steps: 1) Thorough testing of these modules is left. I will begin thorough testing from Monday when Florent will be back to his office. 2) I will also try to complete documenting my code until then. My next post will contain the final report for this GSoC project. It will contain information to reproduce results, list coded features and possible improvements. 3) I had planned to also plot a statistical eye, but I feel that due to time constraints this wont be possible. I will work on this after GSoC.